文章名稱:Development of Self-Aligned Top-Gate Transistor Arrays on Wafer-Scale Two-Dimensional Semiconductor

期刊名稱:Advanced Science IF:16.3

DOI:10.1002/advs.202415250

【引言】

在二維半導體材料(2DSM)的研究與應用領域,自對準技術對于頂柵場效應晶體管(TG-FET)的發展至關重要。通過精確同步調整柵極與溝道尺寸,自對準技術實現了短溝道集成,從而顯著提升了器件的密度和性能。然而,傳統自對準工藝在晶圓級2DSM TG-FET制備中面臨諸多制約,如制造過程復雜、器件均勻性欠佳以及與大規模集成兼容性不足等問題。

為攻克上述難題,復旦大學相關研究團隊提出了一種創新的自對準方法。該方法結合干法刻蝕、濕法選擇性刻蝕及后優化工藝,基于CVD生長的單層MoS?,成功實現了高性能TG-FET陣列的制備。這一工藝不僅簡化了制造流程,還確保了器件的高度一致性和優異的電學性能。

通過該技術,團隊成功制備出溝道長度僅為200 nm的晶圓級自對準MoS? TG-FET陣列,其開態電流密度高達465.5 μA/m,開關比達到10?,遠超同類傳統器件。基于此陣列,研究者進一步構建了反相器以及NAND和NOR邏輯模塊,充分展示了其在邏輯電路中的應用潛力。這一策略突破了傳統工藝在小型化和集成方面的瓶頸,為2DSM基短溝道器件的規模化制備開辟了新路徑。它不僅顯著提升了二維半導體器件的性能與穩定性,還為未來高密度集成電路及先進電子器件的開發奠定了堅實基礎,展現出重要的應用前景。

【設備助力】

在整個研究過程中,小型臺式無掩膜直寫光刻系統- MicroWriter ML3發揮了至關重要的作用。其具備的精準性能夠滿足短溝道器件對光刻精度的嚴格要求,確保了器件結構的精確制備,有效降低了因光刻誤差導致的器件性能差異。同時,該系統的靈活性使得研究人員可以根據不同的實驗需求,快速調整光刻圖案和參數,提高了研究效率。在制備過程中,研究人員能夠利用其靈活的圖案設計功能,針對不同的器件結構和工藝要求進行光刻,加速了對短溝道器件的制備與優化進程。

小型臺式無掩膜直寫光刻系統- MicroWriter ML3

【圖文導讀】

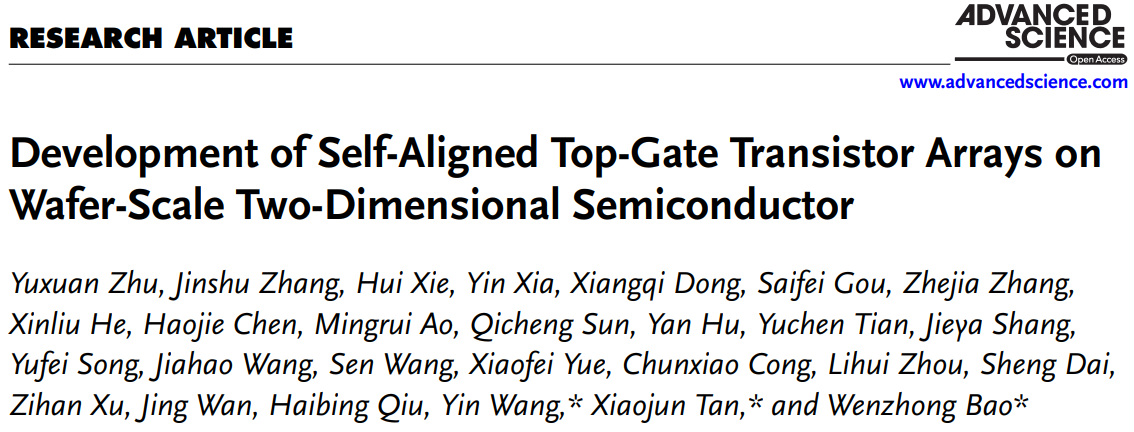

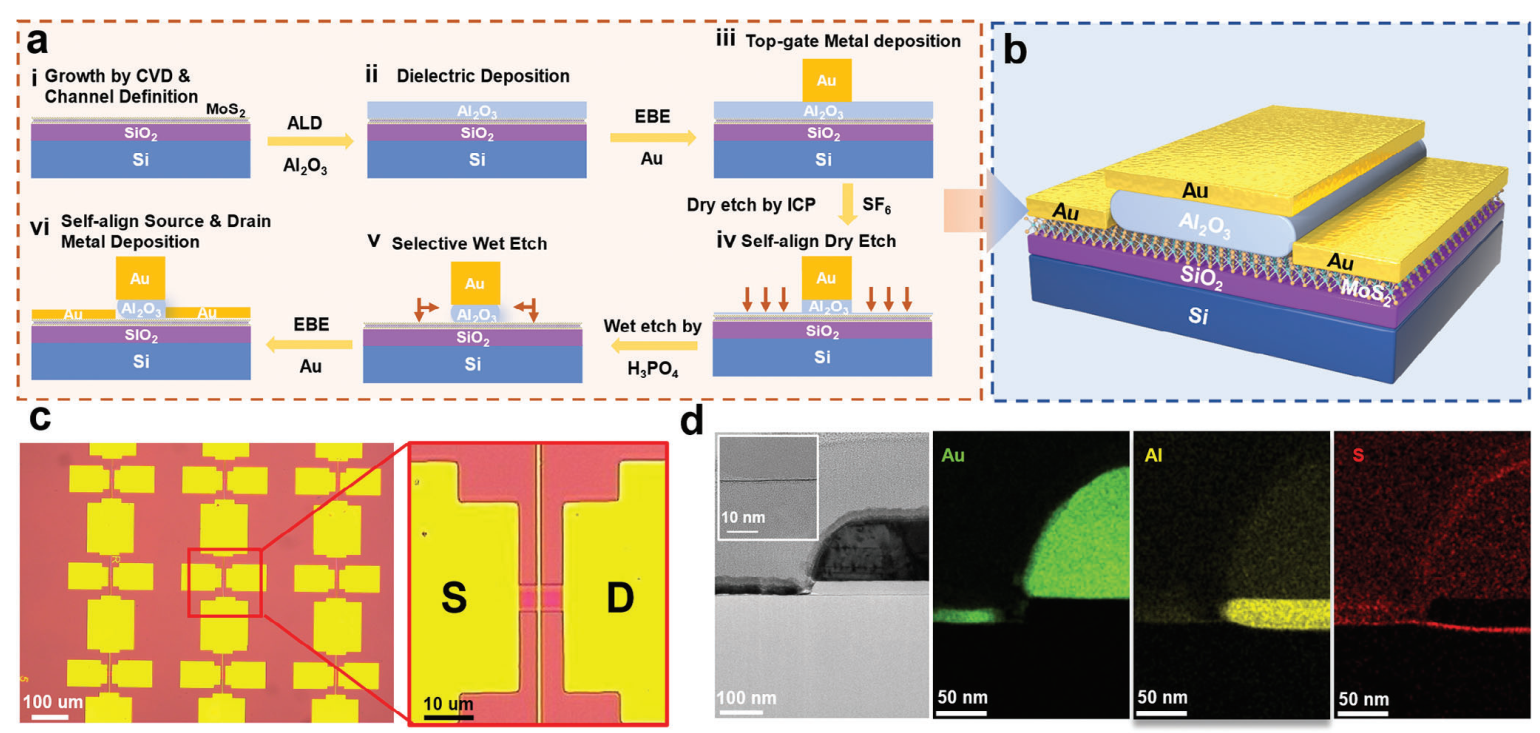

圖1.自對準MoS? TG-FET的制備與結構。(a)自對準MoS? TG-FET制備過程的示意圖。(b)自對準MoS? TG-FET的結構示意圖。(c)自對準MoS? TG-FET陣列的光學圖像。(d)自對準MoS? TG-FET接觸區和柵極區的STEM與EDS圖像。

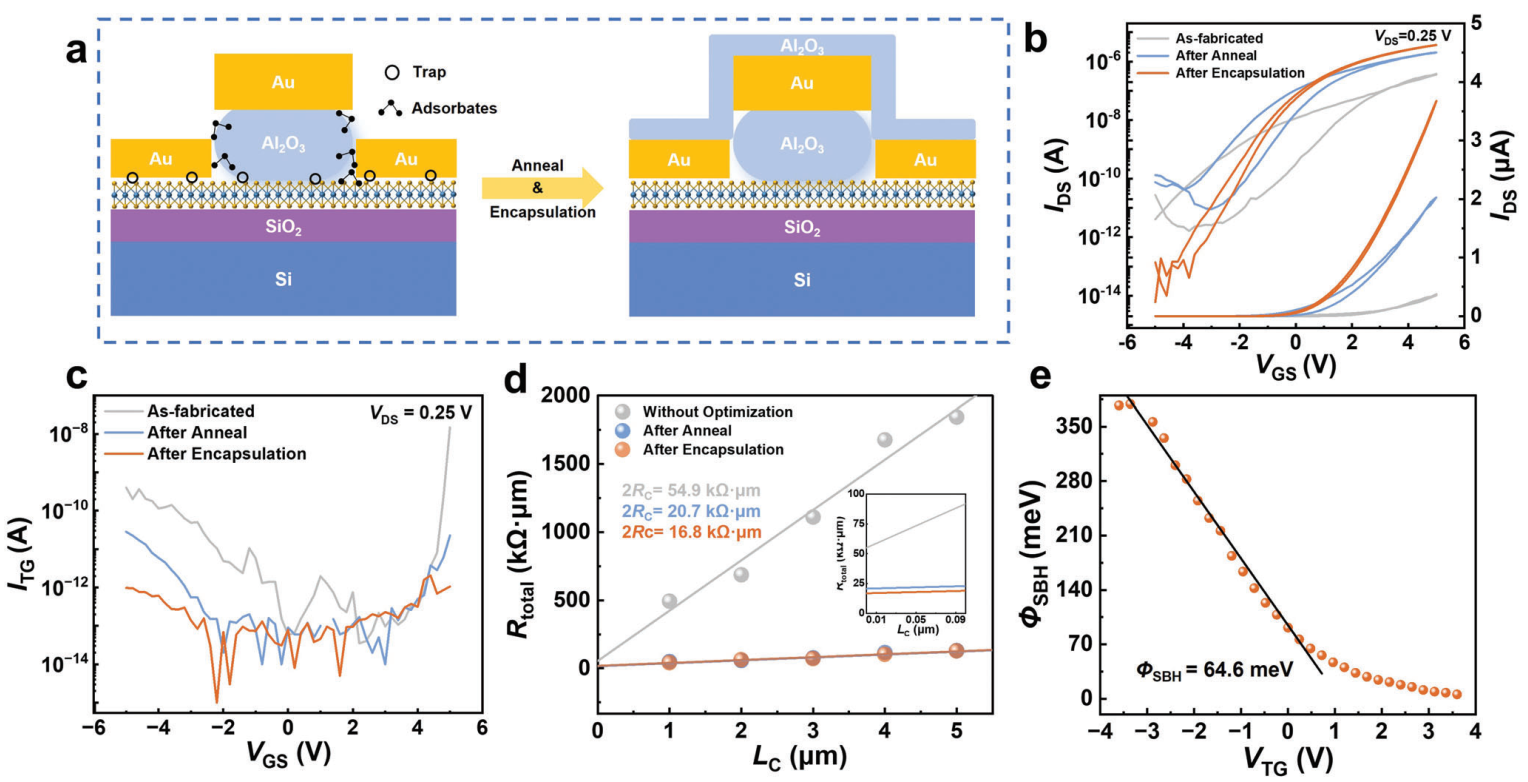

圖2.自對準MoS? TG-FET的示意圖及初始制備與優化后的電學性能。(a)自對準MoS? TG-FET制備過程的示意圖。(b)初始制備的MoS? TG-FET、退火后的MoS? TG-FET及封裝后的MoS? TG-FET的轉移特性。(c)初始制備、退火后及封裝后的MoS? TG-FET的柵極漏電流。(d)初始制備、退火后及封裝后的MoS? TG-FET的接觸電阻。(e)優化后器件的肖特基勢壘高度(SBH)提取結果。

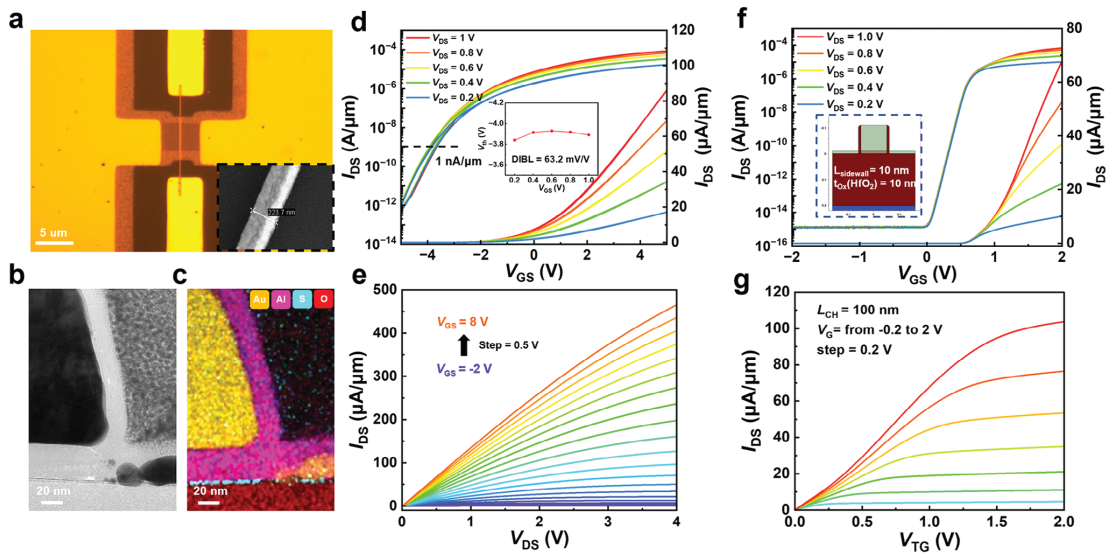

圖3.優化后的自對準MoS? TG-FET的結構及亞微米溝道長度的電學性能。(a)溝道長度約為200 nm的自對準MoS? TG-FET的光學圖像及SEM嵌套圖像。(b)優化后的自對準MoS? TG-FET接觸區的STEM圖像,溝道長度約為200 nm。(c)優化后的自對準MoS? TG-FET接觸區的EDS圖像,溝道長度約為200 nm。(d)溝道長度約為200 nm的MoS? TG-FET的轉移曲線,DIBL(d,嵌圖)及(e)輸出曲線。(f)通過模擬得到的溝道長度為100 nm的自對準MoS? TG-FET的轉移曲線及(g)輸出曲線。

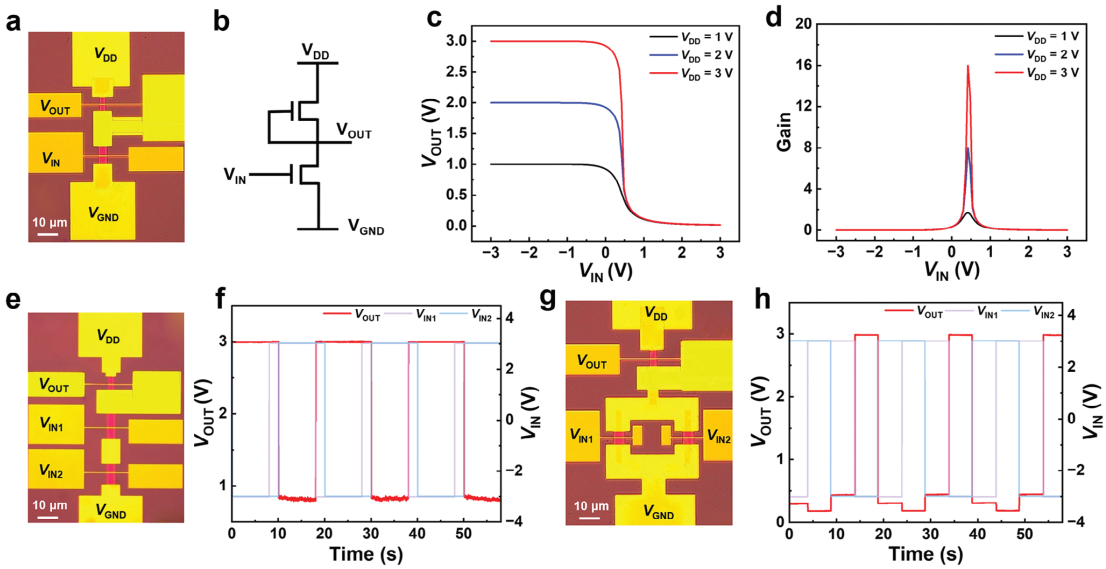

圖4.基于優化后的自對準MoS? TG-FET的電路光學圖像及邏輯功能。(a)反相器的光學圖像及(b)電路圖。(c)反相器在VDD從1 V至3 V時的電壓轉移特性及(d)相應的電壓增益。(e)基于自對準MoS? TG-FET的NAND邏輯電路的光學圖像及(f)NAND邏輯的動態響應。(g)基于自對準MoS? TG-FET的NOR邏輯電路的光學圖像及(h)NOR邏輯的動態響應。

【結論】

綜上所述,復旦大學相關研究團隊通過創新的自對準技術,成功制備了高性能、可擴展的晶圓級MoS? TG-FET陣列,有效解決了傳統自對準工藝在二維半導體器件制備中的難題。

請輸入賬號

請輸入密碼

請輸驗證碼

以上信息由企業自行提供,信息內容的真實性、準確性和合法性由相關企業負責,化工儀器網對此不承擔任何保證責任。

溫馨提示:為規避購買風險,建議您在購買產品前務必確認供應商資質及產品質量。